STM32MP257 U-Boot bmp display does not work with MIPI-DSI 1-lane panel

- December 19, 2025

- 2 replies

- 91 views

Product

STM32MP257DAK3 CPU

Board: Custom board (based on STM32MP257)

Software Environment

U-Boot: from stm32mp-openstlinux-6.6-yocto-scarthgap-mpu-v25.08.27

Boot stage: U-Boot

Display command: bmp display

Display interface: MIPI-DSI

Problem Description

I am using STM32MP257DAK3 with two different MIPI-DSI LCD panels:

Panel A: MIPI-DSI 4 lanes

→ Works correctly in U-Boot using bmp displayPanel B: MIPI-DSI 1 lane

→ Does NOT work in U-Boot using bmp display

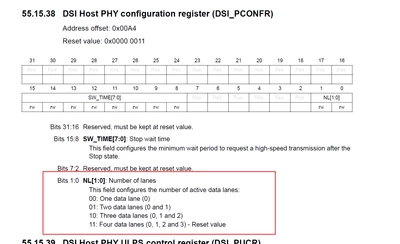

According to the STM32MP25 reference manual, the DSI_PCONFR register supports lane configuration from 1 to 4 lanes.

Therefore, I expect DSI 1-lane mode to be supported by hardware.

However, in U-Boot, the 1-lane panel does not display anything.

Important Clarification

For both panels:

Device Tree is already adapted separately:

Correct dsi,lanes = <4> and dsi,lanes = <1> configuration

Separate panel nodes

Panel drivers are already adapted and validated

Question / Clarification Requested

I would like to confirm:

Does the U-Boot DSI driver (drivers/video/stm32/stm32_dsi.c) officially support MIPI-DSI 1-lane mode?

Is there any limitation, missing configuration, or hard-coded lane setting in the current U-Boot implementation that only supports 4-lane panels?

Is this a known limitation or known issue in the STM32MP25 U-Boot BSP?

Additional Notes

The issue is only observed in U-Boot stage when using bmp display.

No DSI error is printed in U-Boot console.

The DSI PHY and clock configuration are shared between both panels.

Expected Behavior

U-Boot should correctly configure the DSI controller to operate in 1-lane mode.

Request

Please clarify whether:

DSI 1-lane mode is supported in U-Boot for STM32MP257

A patch or workaround is required

Or if this is a known limitation in the current BSP release