32F417: Mapping SPI1 to the SWD debug pins PB3-PB5 - how can this work?

- December 12, 2025

- 8 replies

- 198 views

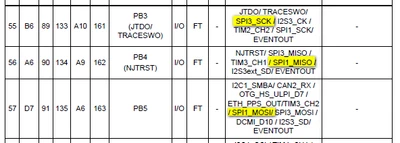

One of the AF options on SPI1 is to use the SWD debug pins PB3-PB5.

How can this be used in reality?

Pretty obviously you can't do SWD breakpoints when SPI1 is thus mapped!

But assuming no SWD debugging is needed, and you use SWD just to program the FLASH, how does one implement this? AFAICT one would need

- on SWD inputs, FLASH loading will work

- on SWD outputs (e.g. SWO - the SWV ITM debug output), FLASH loading works because these pins power up in some mode suitable for SWD FLASH programming.

Then when the code starts running, you will need some logic to disconnect the debugger, so the clock and data SPI signals can come out, without contention with the debugger.

Maybe I am missing something obvious. Or maybe this SPI1 AF mapping option is intended for FLASH programming not via SWD but via a UART, CAN or the weird USB mode.

PB3 may not need anything because the SPI CLK is an output and the SWD SWO signal is also an output