Quad-SPI DDR indirect read mode dummy cycles count

- December 16, 2025

- 1 reply

- 60 views

Hello ST community,

I have some troubles with dummy cycles using Quad-SPI interface in DDR mode on STM32H743 and STM32F746.

I am trying to read data from IS25LP080D QSPI flash with FAST READ QUAD IO DTR MODE OPERATION (0xED command). It is 1-4-4 mode.

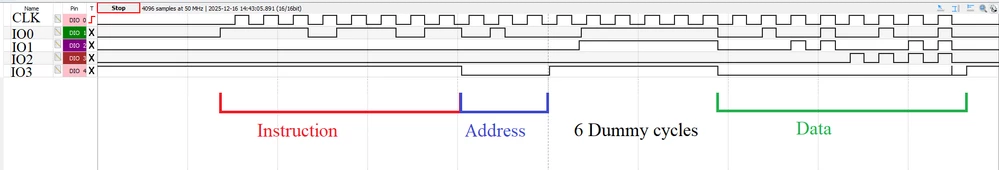

I am having trouble with number of dummy cycles. From IS25LP080D datasheet there must be 6 dummy sclk cycles between address and data. But to get 6 dummy cycles I must set cmd.DummyCycles = 3; in my program. Why there are 3 extra dummy cycles on diagram?

My read function for HAL is below. In this function I set cmd.DummyCycles = 3.

IS25LP_Status_t IS25LP_ReadQuadDDR(QSPI_HandleTypeDef *hqspi, uint8_t *buf, uint32_t addr, uint32_t size)

{

QSPI_CommandTypeDef cmd = {0};

cmd.InstructionMode = QSPI_INSTRUCTION_1_LINE;

cmd.Instruction = IS25LP_FAST_READ_QUAD_IO_DDR;

cmd.AddressMode = QSPI_ADDRESS_4_LINES;

cmd.AddressSize = QSPI_ADDRESS_24_BITS;

cmd.Address = addr;

cmd.AlternateByteMode = QSPI_ALTERNATE_BYTES_NONE;

cmd.AlternateBytesSize = QSPI_ALTERNATE_BYTES_24_BITS;

cmd.AlternateBytes = 0x0;

cmd.DummyCycles = 3;

cmd.DataMode = QSPI_DATA_4_LINES;

cmd.NbData = size;

cmd.DdrMode = QSPI_DDR_MODE_ENABLE;

cmd.DdrHoldHalfCycle = QSPI_DDR_HHC_HALF_CLK_DELAY;

cmd.SIOOMode = QSPI_SIOO_INST_EVERY_CMD;

if (HAL_QSPI_Command(hqspi, &cmd, QSPI_TIMEOUT) != HAL_OK) {

return IS25LP_ERROR;

}

if (HAL_QSPI_Receive(hqspi, buf, QSPI_TIMEOUT) != HAL_OK) {

return IS25LP_ERROR;

}

return IS25LP_OK;

}In my main.c I use this function to read 8 bytes of data:

status = IS25LP_ReadQuadDDR(&hqspi, readBuf, 0x1000, 8);And I am getting correct flash data:

First 8 bytes (DDR): 00 01 02 03 04 05 06 07

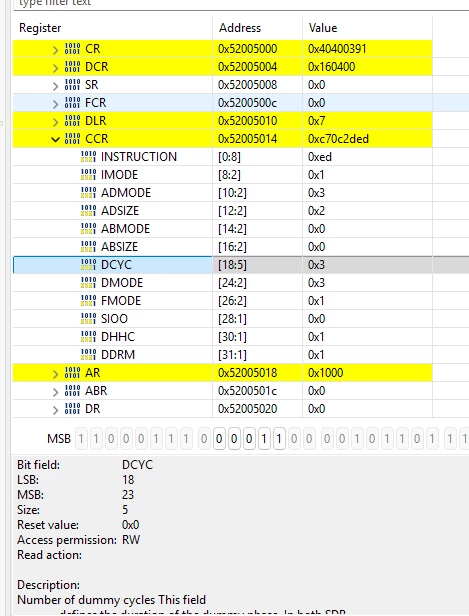

DCYC field in CCR register is 0x3, so there must be only 3 dummy cycles.

But on time diagram I can see 6 dummy cycles:

So I got 3 extra dummy cycles on STM32H743 board.

My question is: why there are extra dummy cycles? How should I calculate there number?

I also tried this code on STM32F746 board and I got 1 extra dummy cycles, but not 3.

Thank you for any thoughts!

I'm attaching my main.c and is25lp_mem.c for the reference.

Processor: STM32H743ZI

Board: Nucleo-H743ZI

Driver version: STM32Cube MCU Package for STM32H7 1.12.0

Compiler: GNU Tools for STM32 (12.3.rel1)

Cube MX 6.13.0